TLK2226

SLLS689D-JANUARY 2006-REVISED DECEMBER 2006

# 6 PORT GIGABIT ETHERNET TRANSCEIVER

## FEATURES

STRUMENTS

- Six 1.25 Gigabits Per Second (Gbps) Synchronizable Transceivers (Support for 100 Mbps 100Base-FX Mode)

- Configurable 1, 2, 3, 4, 5, or 6 Port Operation via MDIO

- Low Power Consumption <1.5W at 1.25Gb/sec

- IEEE 802.3z Gigabit Ethernet Compliant

- Differential VML Transmit Outputs With no

External Components Necessary

- Programmable High Speed Output Pre-Emphasis Levels

- Nibble Wide RTBI/RGMII Compliant Interface

- Selectable Clock Tolerance Compensation

- Selectable on Chip Physical Coding Sublayer (PCS) Functions Including 8b/10b IEEE 802.3z Compliant Encoder and Decoder

- 1/10<sup>th</sup> Rate Capability for 125 Mbps Operation With Automatic Rate Sense Capability

- JEDEC 1.5V HSTL (Extendable to 1.8 V) on Parallel Data Busses

- JEDEC 1.8/2.5/3.3 V LVCMOS on REFCLK and Control Pins

- Internal Series Termination on HSTL Outputs to Drive 50  $\Omega$  Lines

- Standard Parallel Interface Timing:

- Source Centered/Aligned Timing on Inputs

- Source Centered/Aligned Timing on Outputs

- Comprehensive Suite Of Built-In Testability

- IEEE 802.3 Clause 22 Management Data Interface (MDIO) Support

- IEEE 1149.1 JTAG Support

- Hot Plug Protection on Serial I/O

- No External Filter Components Required for PLLs

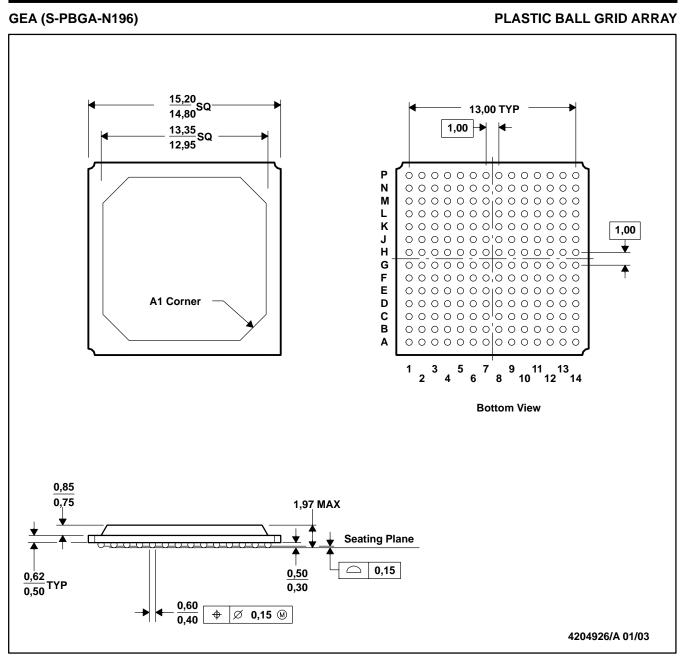

- Small Footprint 15  $\times$  15 mm, 196-Pin, 1,0 mm Ball Pitch BGA

- Advanced Low Power 0.18 μm CMOS Technology

- Commercial Temperature Rating (0°C to 70°C)

- Repeater Mode:

- In the Serial Domain Using Recovered Clock (Non-Retiming)

- In the Parallel Domain Using REFCLK (Retiming)

- Jumbo Packet (9300 Byte) Support

- Clause 36A Test Pattern Gen/Ver

- SGMII Mode Support (10/100/1000 Mbps)

- Parallel Port Swap Mode

## FUNCTIONAL OVERVIEW

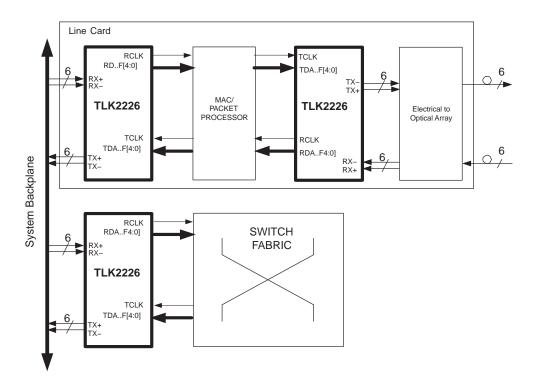

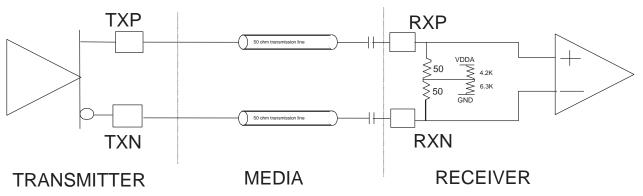

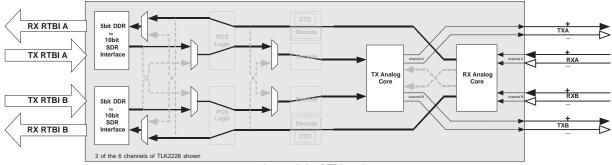

The TLK2226 is the third generation of Gigabit Ethernet transceivers from Texas Instruments combining high port density and ultra-low power in a small form factor footprint. The TLK2226 provides for high-speed full-duplex point-to-point data transmissions based on the IEEE802.3z 1000Mbps Ethernet specification. The TLK2226 supports data rates from 1.0 Gbps through 1.3 Gbps. Each channel is capable of operating at 125 Mbps for IEEE Ethernet 100FX mode, and the rate for each channel may be set through MDIO or automatically sensed and set by the TLK2226.The primary application of this device is to provide building blocks for developing point-to-point baseband data transmission over controlled impedance media of 50  $\Omega$ . The transmission media can be printed circuit board traces, copper cables or fiber-optical media. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling to the environment.

This device performs the data encoding, decoding, serialization, deserialization, clock extraction and clock tolerance compensation functions for a physical layer interface device. Each channel operates at up to 1.3 Gbps providing up to 7.5 Gbps of aggregate data bandwidth over a copper or optical media interface.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

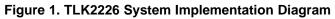

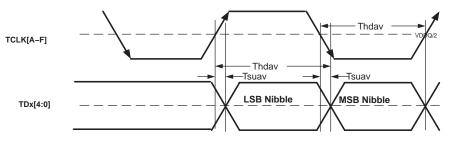

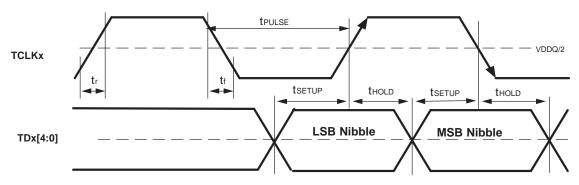

The TLK2226 has six channels of SERDES each with 5 bit busses clocked double data rate (DDR). The parallel interface accepts un-encoded or 5-bit wide encoded data aligned to both the rising and falling edge of the transmit clock. The data is clocked low-order bits first, (i.e. bits 0–4 of the 8b/10b encoded data) on the rising edge of the transmit clock and the high-order bits (i.e. bits 5–9 of the 8b/10b encoded data) are clocked on the falling edge of the clock. The receive path interface is clocked in the same manner.

The TLK2226 supports two modes that can repeat data from a channel's serial receiver to the adjacent channel's serial transmitter: serial repeater mode and retiming repeater mode. In serial repeater mode, the clock/data recovery (CDR) function will lock onto the incoming data stream and will pass this data stream over to the adjacent channel to be retransmitted. In serial repeater mode, the data stream stays in the same clock domain as the incoming data; there is no clock tolerance compensation function performed to align the data stream to the reference clock domain. In retiming repeater mode, the CDR function will lock onto the incoming data stream but the data will be deserialized and passed through the CTC FIFO and then serialized for transmission on the adjacent channel. In both repeater modes, the received data for Channel A is retransmitted on the output for channel B while the received data for Channel B is retransmitted on the output for Channel A. Likewise, Channel C is paired with Channel D, and Channel E is paired with Channel F. The repeater modes can be enabled on a channel by channel basis through the use of register control bits programmed through the MDIO interface.

The recovered data clock frequency can be aligned to the reference clock on each channel by means of a clock tolerance compensation circuit and internal FIFO that will insert or drop Idle 20-bit IDLE codes as needed in the absence of data. The received data for all channels are aligned to a single receive data clock that is a buffered version of the reference clock.

The TLK2226 supports a selectable IEEE802.3z compliant 8b/10b encoder/decoder in all its 1.25Gbps modes of operation, and a IEEE802 compliant 4b/5b encoder/decoder in its 125Mbps mode of operation.

The TLK2226 supports selectable RTBI and RGMII interface to supervision ASIC.

The TLK2226 automatically locks onto incoming data without the need to pre-lock.

Detection of whether the incoming data stream is at 1.25 Gbps or 125 Mbps data rate is automatic.

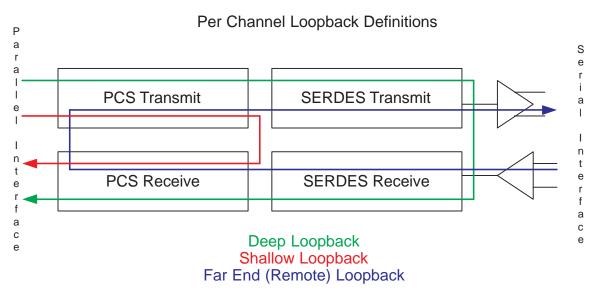

A comprehensive series of built-in tests for self-test purposes including loopback and PRBS generation and verification is provided. An IEEE 1149.1 JTAG port is also supported to aid in board manufacturing test.

This device is housed in a small form factor  $15 \times 15$  mm, 196-pin, BGA with 1,0 mm ball pitch and is characterized to support the commercial temperature range of 0°C to 70°C.

Expect the TLK2226 to consume less than 1.5 W, when operating at 1.25 Gbps.

The TLK2226 is designed to be hot plug capable. A power-on reset puts the parallel side output signal pins in a high-impedance state during power-up as well as pulls both TX+ and TX- to VDDA through 500  $\Omega$ .

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                      |                   |                                     | VALUE             | UNIT |

|----------------------|-------------------|-------------------------------------|-------------------|------|

| V <sub>DDQ</sub>     | I/O Supply volta  | age <sup>(2)</sup>                  | -0.3 to 2.5       | V    |

| V <sub>DDS</sub>     | I/O Supply volta  | age <sup>(2)</sup>                  | -0.3 to 3.6       | V    |

| $V_{DD}$ , $V_{DDA}$ | Core Supply vo    | Itage <sup>(2)</sup>                | -0.3 to 2.5       | V    |

| V                    |                   | LVCMOS                              | -0.5 to 3.6       | - V  |

| VI                   | Input voltage     | HSTL                                | -0.5 to 2.5       | v    |

|                      | DC Input voltag   | e (I/O)                             | -0.3 to 2.5       | V    |

|                      | Storage temper    | ature                               | -65 to 85         | °C   |

|                      | Electrostatic dis | scharge                             | HBM: 2KV, CDM:750 | V    |

|                      | Characterized f   | ree-air operating temperature range | 0 to 70           | °C   |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential I/O bus voltages, are with respect to network ground terminal

## **RECOMMENDED OPERATING CONDITIONS**

|                  |                                        |                                                                | MIN   | NOM  | MAX   | UNIT |

|------------------|----------------------------------------|----------------------------------------------------------------|-------|------|-------|------|

| $V_{DD}$         | Core supply voltage                    | Peak-peak AC noise in the 1–10 MHz range may not exceed 100 mV | 1.7   | 1.8  | 1.9   | V    |

| M                |                                        | 1.5 V HSTL Class 1 peak-peak AC noise may not exceed 150 mV    | 1.4   | 1.5  | 1.6   | V    |

| V <sub>DDQ</sub> | HSTL I/O supply voltage                | 1.8 V HSTL Class 1 peak-peak AC noise may not exceed 150 mV    | 1.7   | 1.8  | 1.9   | V    |

|                  |                                        | 1.8 V CMOS peak-peak AC noise may not exceed 150 mV            | 1.7   | 1.8  | 1.9   | V    |

| V <sub>DDS</sub> | LVCMOS I/O supply voltage              | 2.5 V CMOS peak-peak AC noise may not exceed 150 mV            | 2.375 | 2.5  | 2.625 | V    |

|                  |                                        | 3.3 V CMOS peak-peak AC noise may not exceed 150 mV            | 3.14  | 3.3  | 3.47  | V    |

| V <sub>DDA</sub> | Analog supply voltage                  | Peak-peak AC noise in the 1–10 MHz range may not exceed 100 mV | 1.7   | 1.8  | 1.9   | V    |

| V                | Input reference voltage <sup>(1)</sup> | 1.5 V HSTL Class 1                                             | 0.7   | 0.75 | 0.8   | V    |

| V <sub>REF</sub> | input reference voltage.               | 1.8 V HSTL Class 1                                             | 0.85  | 0.9  | 0.95  | v    |

| I <sub>DD</sub>  | Core supply current                    | $R_{\omega}$ = 125 MHz, $V_{DD}$ = 1.8 V                       |       |      | 390   | mA   |

|                  | HSTL I/O supply current                | $R_{\omega}$ = 125 MHz, $V_{DDQ}$ = 1.5 V                      |       |      | 146   | mA   |

| I_HSTL           |                                        | $R_{\omega}$ = 125 MHz, $V_{DDQ}$ = 1.8 V                      |       |      | 204   | ША   |

|                  |                                        | $R_{\omega}$ = 125 MHz, $V_{DDS}$ = 1.8 V                      |       |      | 1     |      |

| I <sub>DDS</sub> | LVCMOS I/O supply current              | $R_{\omega}$ = 125 MHz, $V_{DDS}$ = 2.5 V                      |       |      | 3     | mA   |

|                  |                                        | $R_{\omega}$ = 125 MHz, $V_{DDS}$ = 3.3 V                      |       |      | 7     |      |

| I <sub>DDA</sub> | Analog supply current                  | $R_{\omega}$ = 125 MHz, $V_{DDA}$ = 1.8 V                      |       |      | 183   | mA   |

| PD               | Total power consumption                | $R_{\omega}$ = 125 MHz, $V_{DDQ}$ = 1.8 V                      |       |      | 1.50  | W    |

| I <sub>DDQ</sub> | Shutdown current                       | ENABLE = low                                                   |       | 30   |       | mA   |

(1) Typically, the value of VREF is expected to be 0.5 V<sub>DDQ</sub> of the transmitting device and V<sub>REF</sub> is expected to track variations in V<sub>DDQ</sub>.

## LVCMOS ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

over recommended operating conditions (unless otherwise noted)

|                 | PARAMETER                 | TEST CONDITIONS                           | MIN                    | TYP | MAX              | UNIT |

|-----------------|---------------------------|-------------------------------------------|------------------------|-----|------------------|------|

| V <sub>OH</sub> | High-level output voltage | $I_{OH} = -400 \ \mu A$ , $V_{DDS} = MIN$ | V <sub>DDS</sub> - 0.2 |     | V <sub>DDS</sub> | V    |

(1) Unused inputs that do not hold an integrated pull up or pull down circuit need to be terminated to either GND or VDDQ respectively to avoid extensive currents and life time degradation.

## LVCMOS ELECTRICAL CHARACTERISTICS (continued)

over recommended operating conditions (unless otherwise noted)

|                 | PARAMETER                | TEST CONDITIONS                               | MIN  | TYP  | MAX                   | UNIT |

|-----------------|--------------------------|-----------------------------------------------|------|------|-----------------------|------|

| V <sub>OL</sub> | Low-level output voltage | $I_{OL} = 1 \text{ mA}, V_{DDS} = \text{MIN}$ | 0    | 0.25 | 0.5                   | V    |

|                 |                          | V <sub>DDS</sub> = 1.8 V                      | 1.4  |      | V <sub>DDS</sub> +0.2 |      |

| VIH             | High-level input voltage | V <sub>DDS</sub> = 2.5 V                      | 1.55 |      | V <sub>DDS</sub> +0.2 | V    |

|                 |                          | V <sub>DDS</sub> = 3.3 V                      | 2.0  |      | V <sub>DDS</sub> +0.2 |      |

|                 |                          | V <sub>DDS</sub> = 1.8 V                      | -0.2 |      | 0.63                  |      |

| V <sub>IL</sub> | Low-level input voltage  | V <sub>DDS</sub> = 2.5 V                      | -0.2 |      | 0.7                   | V    |

|                 |                          | V <sub>DDS</sub> = 3.3 V                      | -0.2 |      | 1.4                   |      |

| I <sub>H</sub>  | High input current       | $V_{DDS} = MAX, V_{IN} = 2.0 V$               |      |      | 400                   | μΑ   |

| ۱ <sub>L</sub>  | Low input current        | $V_{DDS} = MAX, V_{IN} = 2.0 V$               |      |      | -600                  | μΑ   |

| CIN             | Input capacitance        |                                               |      |      | 4                     | pF   |

## HSTL ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                 | TEST CONDITIONS                               | MIN                    | TYP                    | MAX                    | UNIT |

|---------------------|---------------------------|-----------------------------------------------|------------------------|------------------------|------------------------|------|

| V <sub>OH(dc)</sub> | High-level output voltage | DC output, logic high                         | V <sub>DDQ</sub> -0.4  |                        | V <sub>DDQ</sub>       | V    |

| V <sub>OL(dc)</sub> | Low-level output voltage  | DC output, logic low                          |                        |                        | 0.4                    | V    |

| V <sub>IH(dc)</sub> | High-level input voltage  | DC input, logic high                          | V <sub>REF</sub> +0.10 |                        | V <sub>DDQ</sub> +0.3  | V    |

| V <sub>IL(dc)</sub> | Low-level input voltage   | DC input, logic low                           | -0.5                   |                        | V <sub>REF</sub> 0.10  | V    |

| M                   |                           | AC input, logic high, $V_{DDQ} = 1.5 V$       | V <sub>REF</sub> +0.20 | V <sub>REF</sub> +0.20 |                        |      |

| V <sub>IH(ac)</sub> | High-level input voltage  | AC input, logic high, $V_{DDQ} = 1.8 V$       | V <sub>REF</sub> +0.35 |                        |                        | V    |

| M                   |                           | AC input, logic low, $V_{DDQ} = 1.5 V$        |                        |                        | V <sub>REF</sub> -0.20 | V    |

| V <sub>IL(ac)</sub> | Low-level input voltage   | AC input, logic low, V <sub>DDQ</sub> = 1.8 V |                        |                        | V <sub>REF</sub> -0.35 | v    |

| I <sub>IH</sub>     | High input current        | Dessiver eski                                 |                        |                        | 10                     |      |

| I <sub>IL</sub>     | Low input current         | Receiver only                                 |                        |                        | ±10                    | μA   |

| I <sub>OH(dc)</sub> | High output current       | V <sub>DDQ</sub> = 1.5 V                      | -8                     |                        |                        | mA   |

| I <sub>OL(dc)</sub> | Low output current        | V <sub>DDQ</sub> = 1.5 V                      | 8                      |                        |                        | mA   |

| C <sub>IN</sub>     | Input capacitance         |                                               |                        |                        | 4                      | pF   |

## **REFERENCE CLOCK TIMING REQUIREMENTS (REFCLK)**<sup>(1)</sup>

over recommended operating conditions (unless otherwise noted)

|            | PARAMETER  | TEST CONDITIONS          | MIN       | NOM | MAX       | UNIT             |

|------------|------------|--------------------------|-----------|-----|-----------|------------------|

| $R_\omega$ | Frequency  | Minimum data rate        | TYP-0.01% | 125 | TYP+0.01% | MHz              |

|            | Frequency  | Maximum data rate        | TYP-0.01% | 125 | TYP+0.01% | MHz              |

|            | Accuracy   |                          | -100      |     | 100       | ppm              |

|            | Duty cycle |                          | 40%       | 50% | 60%       |                  |

|            | Jitter     | Random and deterministic |           |     | 40        | ps <sub>pp</sub> |

(1) This clock should be crystal referenced to meet the requirements of this table (Contact TI for specific clocking recommendations). Rate activity of REFCLK is internally monitored. As soon as REFCLK is disconnected the device will initiate a global power-down mode; PLLs will be turned off, output divers disabled and other current sources such as pull-up's and pull down's will be disabled to avoid power consumption. To re-activate the device, restart REFCLK.

## SERIAL TRANSMITTER/RECEIVER CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                               | TEST CONDITIONS                                                                                        | MIN              | TYP              | MAX              | UNIT  |

|---------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|-------|

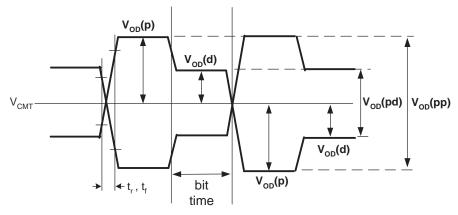

|                     |                                                         | Pre-Emphasis 16.1:0 = 11. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 650              | 950              | 1250             | mV    |

| V <sub>OD(p)</sub>  | TX output voltage magnitude                             | Pre-Emphasis 16.1:0 = 10. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 625              | 900              | 1125             | mV    |

|                     | TX Amp. Control 16.14 = 1                               | Pre-Emphasis 16.1:0 = 01. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 575              | 850              | 1075             | mV    |

| V <sub>OD(d)</sub>  |                                                         | Pre-Emphasis 16.1:0 = 00. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 550              | 800              | 1000             | mV    |

|                     |                                                         | Pre-Emphasis 16.1:0 = 11. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | Not<br>Supported | Not<br>Supported | Not<br>Supported | mV    |

| V <sub>OD(p)</sub>  | TX output voltage magnitude                             | Pre-Emphasis 16.1:0 = 10. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | Not<br>Supported | Not<br>Supported | Not<br>Supported | mV    |

|                     | TX Amp. Control 16.14 = 0                               | Pre-Emphasis 16.1:0 = 01. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 375              | 500              | 675              | mV    |

| V <sub>OD(d)</sub>  |                                                         | Pre-Emphasis 16.1:0 = 00. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 275              | 400              | 500              | mV    |

|                     | TX output differential                                  | Pre-Emphasis 16.1:0 = 11. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 1300             | 1900             | 2500             | mVp-p |

| V <sub>OD(pp)</sub> |                                                         | Pre-Emphasis 16.1:0 = 10. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 1250             | 1800             | 2250             | mVp-p |

|                     | peak-to-peak voltage swing<br>TX Amp. Control 16.14 = 1 | Pre-Emphasis 16.1:0 = 01. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 1150             | 1700             | 2150             | mVp-p |

| V <sub>OD(pd)</sub> |                                                         | Pre-Emphasis 16.1:0 = 00. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 1100             | 1600             | 2000             | mVp-p |

|                     |                                                         | Pre-Emphasis 16.1:0 = 11. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | Not<br>Supported | Not<br>Supported | Not<br>Supported | mVp-p |

| V <sub>OD(pp)</sub> | TX output differential                                  | Pre-Emphasis 16.1:0 = 10. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | Not<br>Supported | Not<br>Supported | Not<br>Supported | mVp-p |

|                     | peak-to-peak voltage swing<br>TX Amp. Control 16.14 = 0 | Pre-Emphasis 16.1:0 = 01. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 750              | 1000             | 1350             | mVp-p |

| V <sub>OD(pd)</sub> |                                                         | Pre-Emphasis 16.1:0 = 00. See Figure 3.<br>Differential and common-mode output<br>voltage definitions. | 550              | 800              | 1000             | mVp-p |

| V <sub>CMT</sub>    | TX output common mode voltage range                     | See Figure 3. Differential and common-mode output voltage definitions.                                 | 750              |                  | 1200             | mV    |

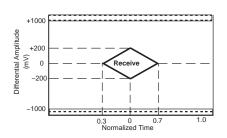

| V <sub>ID</sub>     | RX input voltage magnitude away from common mode        | See Figure 5                                                                                           | 200              |                  | 900              | mV    |

| V <sub>ID(p)</sub>  | RX input differential<br>peak-to-peak voltage swing     | See Figure 5                                                                                           | 400              |                  | 2500             | mVp-p |

| I <sub>LKG</sub>    | RX input leakage current                                |                                                                                                        | -10              |                  | 10               | μA    |

| CI                  | RX input capacitance                                    |                                                                                                        |                  |                  | 2                | pF    |

## SERIAL TRANSMITTER/RECEIVER CHARACTERISTICS (continued)

over operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                                                  | TEST CONDITIONS                                                                                   | MIN | TYP  | MAX   | UNIT              |

|---------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|------|-------|-------------------|

|                                 | Differential output signal rise                            | $R_L = 50 \Omega$ , $C_L = 5 pF$ , See Figure 3                                                   |     | 150  | 220   | ps                |

| t <sub>r</sub> , t <sub>f</sub> | Differential output signal rise,<br>fall time (20% to 80%) | $R_L = 50 \Omega$ , $C_L = 5 pF$ , See Figure 3 For Half amplitude condition without Pre-Emphasis |     | 165  | 260   | ps                |

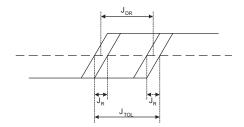

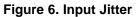

| J <sub>TOL</sub>                | Jitter Tolerance, Total Jitter at Serial Input             | Zero crossing, See Figure 6                                                                       |     |      | 0.75  | UI <sup>(1)</sup> |

| J <sub>DR</sub>                 | Serial Input Deterministic<br>Jitter                       | Zero crossing, See Figure 6                                                                       |     |      | 0.462 | UI                |

| J <sub>T</sub>                  | Serial Output Total Jitter<br>Alternating disparity        | K28.5 1.25 Gbps                                                                                   |     | 0.15 | 0.24  | UI                |

| J <sub>D</sub>                  | Serial Output Deterministic<br>Jitter                      | Alternating disparity K28.5 1,25 Gbps                                                             |     |      | 0.10  | UI                |

| R <sub>(LATENCY)</sub>          | From MDI /T/ to RGMII<br>RX_DV<br>de-assert                | 1000Base-X Operating Mode                                                                         |     |      | 192   | Bits              |

| T <sub>(LATENCY)</sub>          | From the assertion of TX_EN to MDI output of /S/           |                                                                                                   |     |      | 136   | Bits              |

| R <sub>(LATENCY)</sub>          | MDI Input to RX_DV<br>de-assert                            | 100Rose EX Operating Mode                                                                         |     |      | 32    | Bits              |

| T <sub>(LATENCY)</sub>          | TX_EN sampled to MDI output                                | 100Base-FX Operating Mode                                                                         |     |      | 14    | Bits              |

(1) Unit Interval = one serial bit time (min 800 ps)

Figure 3. Differential and Common-Mode Output Voltage Definitions

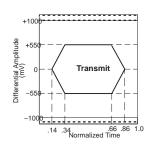

Figure 4. Transmit Template

Figure 5. Receive Template

NOTE:  $J_{TOL} = J_R + J_{DR}$ , where  $J_{TOL}$  is the receive jitter tolerance,  $J_{DR}$  is the received deterministic jitter, and  $J_R$  is the Gaussian random edge jitter distribution at a maximum BER = 10<sup>-12</sup>.

## HSTL OUTPUT SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                   | PARAMETER                                                             | TEST CONDITION                                                 | MIN | NOM | MAX | UNIT |

|-------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|-----|-----|-----|------|

| Tr                | Clock and data rise time                                              | 80% to 20% output voltage, see Figure 7, $C = 10 \text{ pF}$   |     |     | 1.5 | ns   |

| T <sub>f</sub>    | Clock and data fall time                                              | 80% to 20% output voltage, see Figure 7,<br>C = 10 pF          |     |     | 1.8 | ns   |

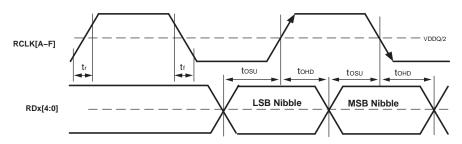

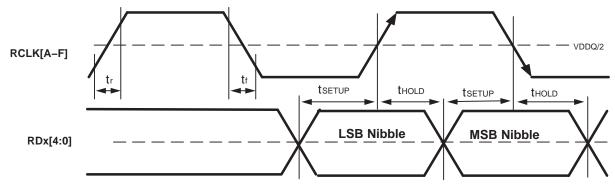

| T <sub>OSU</sub>  | RD[4:0] valid (setup) prior to RCLK transition high or low            | See Figure 7, timing relative to 0.5×VDDQ, 25 MHz and 125 MHz  | 1.2 |     |     | ns   |

| T <sub>OHD</sub>  | RD[4:0] valid (hold) after RCLK transition high or low                | See Figure 7, timing relative to 0.5×VDDQ, 25 MHz and 125 MHz  | 1.2 |     |     | ns   |

| T <sub>suav</sub> | RCLK transition high or low to data valid window beginning (RD[4:0]). | See Figure 8, timing relative to 0.5×VDDQ, 25 MHz and 125 MHz  |     |     | 800 | ps   |

| T <sub>hdav</sub> | RCLK transition high or low to data valid window ending (RD[4:0]).    | See Figure 8 , timing relative to 0.5×VDDQ, 25 MHz and 125 MHz | 3.2 |     |     | ns   |

Figure 7. HSTL Receive Output Timing Requirements (Centered)

Figure 8. HSTL Receive Output Timing Requirements (Aligned)

## HSTL INPUT TIMING REQUIREMENTS

over recommended operating conditions (unless otherwise noted)

|                   | PARAMETER                                                             | TEST CONDITION                                             | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|-------------------|-----------------------------------------------------------------------|------------------------------------------------------------|-----|--------------------|-----|------|

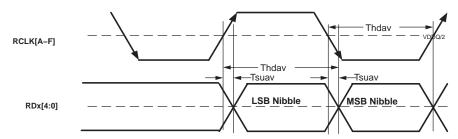

| T <sub>ISU</sub>  | TDx[4:0] setup prior to TCLK transition<br>high or low                | Figure 19 timing relative to 0.5×VDDQ, 25 MHz and 125 MHz  | 0.6 |                    |     | ns   |

| T <sub>IHD</sub>  | TDx[4:0] hold after TCLK transition high or low                       | Figure 19, timing relative to 0.5×VDDQ, 25 MHz and 125 MHz | 0.6 |                    |     | ns   |

| T <sub>suav</sub> | RCLK transition high or low to data valid window beginning (RD[4:0]). | Figure 18, timing relative to 0.5×VDDQ, 25 MHz and 125 MHz |     |                    | 1.4 | ns   |

| T <sub>hdav</sub> | RCLK transition high or low to data valid window ending (RD[4:0]).    | Figure 18, timing relative to 0.5×VDDQ, 25 MHz and 125 MHz | 2.6 |                    |     | ns   |

(1) All typical values are at 25°C and with a nominal supply.

Figure 9. HSTL Data Input Timing Requirements (Centered)

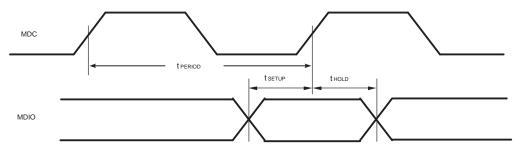

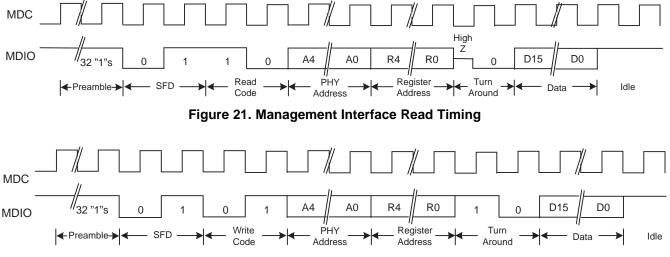

## **MDIO TIMING REQUIREMENTS**

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                   | TEST CONDITIONS | MIN | NOM M | AX  | UNIT |

|---------------------|-----------------------------|-----------------|-----|-------|-----|------|

| t <sub>period</sub> | MDC period                  | See Figure 11   | 400 |       |     | ns   |

| t <sub>setup</sub>  | MDIO setup to ↑ MDC         | See Figure 11   | 10  |       |     | ns   |

| t <sub>hold</sub>   | MDIO hold to $\uparrow$ MDC | See Figure 11   | 10  |       |     | ns   |

| T <sub>data</sub>   | MDC ↑ to MDIO valid         |                 | 0   | 3     | 300 | ns   |

Figure 11. MDIO Read/Write Timing

Figure 12. Example High Speed I/O AC Coupled Mode

TEXAS INSTRUMENTS www.ti.com

#### SLLS689D-JANUARY 2006-REVISED DECEMBER 2006

|    | А     | В    | С     | D    | E           | F          | G     | Н          | J    | К           | L    | М     | Ν    | Ρ     |    |

|----|-------|------|-------|------|-------------|------------|-------|------------|------|-------------|------|-------|------|-------|----|

| 14 | GNDA  | GNDA | GNDA  | GNDA | GNDA        | GNDA       | GNDA  | GNDA       | GNDA | GNDA        | GNDA | GNDA  | GNDA | GNDA  | 14 |

| 13 | TXA+  | RXA+ | RXB+  | TXB+ | GNDA        | TXC+       | RXC+  | RXD+       | TXD+ | GNDA        | TXE+ | RXE+  | RXF+ | TXF+  | 13 |

| 12 | TXA-  | RXA– | RXB-  | TXB- | VDDA        | TXC-       | RXC-  | RXD-       | TXD- | VDDA        | TXE- | RXE-  | RXF– | TXF-  | 12 |

| 11 | VDDA  | VDDA | VDDA  | VDDA | VDDA        | VDDA       | VDD   | VDD        | VDDA | VDDA        | VDDA | VDDA  | VDDA | VDDA  | 11 |

| 10 | TDA0  | TDA1 | TDA2  | TDA3 | RESET       | VDD        | VDD   | VDD        | VDD  | SYNC<br>EN  | TDF3 | TDF2  | TDF1 | TDF0  | 10 |

| 9  | TCLKA | VDDQ | TDA4  | RDA4 | EN-<br>ABLE | GND        | GND   | GND        | GND  | DVAD4       | RDF4 | TDF4  | VDDQ | TCLKF | 9  |

| 8  | RDA0  | GND  | RDA3  | VDDQ | TCLK<br>SEL | GND        | GND   | GND        | GND  | DVAD3       | VDDQ | RDF3  | GND  | RDF0  | 8  |

| 7  | RCLKA | RDA1 | RDA2  | GND  | SGMII       | GND        | GND   | GND        | GND  | SWAP        | GND  | RDF2  | RDF1 | RCLKF | 7  |

| 6  | TDB0  | VDDQ | TDB1  | TDB2 | CODE        | GND        | GND   | GND        | GND  | REPEA<br>TB | TDE2 | TDE1  | VDDQ | TDE0  | 6  |

| 5  | TCLKB | GND  | TDB3  | VDDQ | LPBK        | PRBSE<br>N | TRSTN | CTC_E<br>N | RSVD | REPEA<br>TA | VDDQ | TDE3  | GND  | TCLKE | 5  |

| 4  | RDB0  | RDB1 | TDB4  | GND  | RDC2        | RDC4       | TDI   | TDO        | RDD4 | RDD2        | GND  | TDE4  | RDE1 | RDE0  | 4  |

| 3  | RCLKB | VDDQ | RDB2  | RDB3 | RDC1        | RDC3       | TCLK  | TMS        | RDD3 | RDD1        | RDE3 | RDE2  | VDDQ | RCLKE | 3  |

| 2  | RDB4  | GND  | TDC2  | TDC4 | RDC0        | MDIO       | VREF  | GND        | VDDS | RDD0        | TDD4 | TDD2  | GND  | RDE4  | 2  |

| 1  | TDC0  | TDC1 | TCLKC | TDC3 | RCLKC       | MDC        | VDDS  | REFCL<br>K | GND  | RCLKD       | TDD3 | TCLKD | TDD1 | TDD0  | 1  |

|    | A     | В    | С     | D    | E           | F          | G     | Н          | J    | К           | L    | М     | N    | Р     | I  |

NOTE: Unused inputs that do not hold an integrated pull up or pull down circuit need to be terminated to either GND or VDDQ respectively to avoid extensive currents and life time degradation.

Figure 13. Terminal Diagram

## SIGNAL TERMINAL DESCRIPTION

| SIGNAL                                                                           | LOCATION                                                                  | TYPE                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Serial I/O Signa                                                                 | als                                                                       |                              | ·                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| TXA+, TXA–<br>TXB+, TXB–<br>TXC+, TXC–<br>TXD+, TXD–<br>TXE+, TXE–<br>TXF+, TXF– | A13, A12,<br>D13, D12,<br>F13, F12,<br>J13, J12,<br>L13, L12,<br>P13, P12 | VML Output                   | <b>Differential Output Transmit</b> . TX[A-F]+ and TX[A-F]- are differential serial outputs that interface to a copper or an optical I/F module. TX[A-F]+ and TX[A-F]- are pulled to VDDA through 500 ohms when LPBK = high or when the LOOPBACK (deep only) bit for a particular channel in the MDIO registers is set.                                                                  |  |  |  |  |  |  |  |

| RXA+, RXA-<br>RXB+, RXB-<br>RXC+, RXC-<br>RXD+, RXD-<br>RXE+, RXE-<br>RXF+, RXF- | B13, B12,<br>C13, C12,<br>G13, G12,<br>H13, H12,<br>M13, M12,<br>N13, N12 | PECL-<br>compatible<br>Input | <b>Differential input receive.</b> RX[A-F]+ and RX[A-F]- are the differential serial input interface from a copper or an optical I/F module. Differential resistive termination is built-in for these terminals.                                                                                                                                                                         |  |  |  |  |  |  |  |

| Transmit Data                                                                    | Bus and Clock Sig                                                         | nals                         |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| REFCLK                                                                           | H1                                                                        | LVCMOS Input                 | <b>Reference Clock.</b> REFCLK is an external input clock that provides the clock reference.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| TCLKA,<br>TCLKB,                                                                 | A9,<br>A5,                                                                | HSTL Input                   | Transmit Data Clock Channels A, B, C, D, E, and F.<br>RTBI/RGMII mode:                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| TCLKC,<br>TCLKD,<br>TCLKE,<br>TCLKF                                              | C1,<br>M1,<br>P5,<br>P9                                                   |                              | When in Independent Transmit channel mode (TCLKSEL = 1) these pins<br>are used to latch data for their respective channels on both the rising and<br>falling edges. TCLKA latches data for channel A. TCLKB latches data for<br>channel B. TCLKC latches data for channel C. TCLKD latches data for<br>channel D. TCLKE latches data for channel E. TCLKF latches data for<br>channel F. |  |  |  |  |  |  |  |

|                                                                                  |                                                                           |                              | When in synchronous transmit channel mode (TCLKSEL = 0) only TCLKC is used as the transmit clock for all 6 parallel transmit busses.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| TDA[4:0]                                                                         | C9, D10, C10,<br>B10, A10                                                 | HSTL Input                   | Transmit Data Channel A.<br>RTBI/RGMII mode:                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                                                                                  |                                                                           |                              | The parallel data is clocked into the transceiver on the rising and falling<br>edge of TCLKx and transmitted as a serial stream with TDx0 rising edge<br>data sent as the first bit. Data is input low-order bits first aligned to the risin<br>edge of TCLKx following by high order bits aligned to the falling edge.                                                                  |  |  |  |  |  |  |  |

| TDB[4:0]                                                                         | C4, C5,<br>D6, C6, A6                                                     | HSTL Input                   | Transmit Data Channel B.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| TDC[4:0]                                                                         | D2, D1, C2, B1,<br>A1                                                     | HSTL Input                   | Transmit Data Channel C.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| TDD[4:0]                                                                         | L2, L1, M2, N1,<br>P1                                                     | HSTL Input                   | Transmit Data Channel D.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| TDE[4:0]                                                                         | M4, M5, L6, M6,<br>P6                                                     | HSTL Input                   | Transmit Data Channel E.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| TDF[4:0]                                                                         | M9, L10, M10,<br>N10, P10                                                 | HSTL Input                   | Transmit Data Channel F                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Receive Data E                                                                   | Bus and Clock Sig                                                         | nals                         | ·                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| RCLKA<br>RCLKB                                                                   | A7,<br>A3,                                                                | HSTL Output                  | Individual Receive Byte Clock Channels A through F.<br>RTBI/RGMII mode:                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| RCLKC<br>RCLKD<br>RCLKE<br>RCLKF                                                 | E1,<br>K1,<br>P3,<br>P7                                                   |                              | Recovered byte clock for channels A through F. These clocks are used by the protocol device to latch the received data output for channels A through F. Data is aligned to both the rising and falling edges.                                                                                                                                                                            |  |  |  |  |  |  |  |

|                                                                                  |                                                                           |                              | If the internal CTC FIFO is disabled for a channel, the clock for that channel is 1/10 <sup>th</sup> the clock recovered from the incoming data stream. If CTC is enabled for a channel, the clock for that channel is a buffered version of REFCLK.                                                                                                                                     |  |  |  |  |  |  |  |

|                                                                                  |                                                                           |                              | These pins are internally series terminated to provide direct connection to a $50-\Omega$ transmission line.                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

## SIGNAL TERMINAL DESCRIPTION (continued)

| SIGNAL       | LOCATION              | ТҮРЕ                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|-----------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDA[4:0]     | D9, C8, C7, B7,<br>A8 | HSTL Output              | Receive Data Channel A.<br>RTBI/RGMII mode:                                                                                                                                                                                                                                                                                                                                                     |

|              |                       |                          | Output data is aligned to the rising and falling edge of the RCLKA. Channel data is output low-order bits first aligned to the rising edge of RCLKA followed by high order bits aligned to the falling edge. These pins are internally series terminated to provide direct connection to a $50-\Omega$ transmission line.                                                                       |

| RDB[4:0]     | A2, D3, C3, B4,<br>A4 | HSTL Output              | Receive Data Channel B                                                                                                                                                                                                                                                                                                                                                                          |

| RDC[4:0]     | F4, F3, E4, E3,<br>E2 | HSTL Output              | Receive Data Channel C                                                                                                                                                                                                                                                                                                                                                                          |

| RDD[4:0]     | J4, J3, K4, K3,<br>K2 | HSTL Output              | Receive Data Channel D                                                                                                                                                                                                                                                                                                                                                                          |

| RDE[4:0]     | P2, L3, M3, N4,<br>P4 | HSTL Output              | Receive Data Channel E                                                                                                                                                                                                                                                                                                                                                                          |

| RDF[4:0]     | L9, M8, M7, N7,<br>P8 | HSTL Output              | Receive Data Channel F                                                                                                                                                                                                                                                                                                                                                                          |

| Management   | Data Interface Sign   | als                      |                                                                                                                                                                                                                                                                                                                                                                                                 |

| MDIO         | F2                    | LVCMOS I/O<br>with P/U   | <b>Management Data I/O.</b> MDIO is the bi-directional serial data path for the transfer of management data to and from the protocol device.                                                                                                                                                                                                                                                    |

| MDC          | F1                    | LVCMOS with P/U          | Input Management Data Clock. MDC is the clock reference for the transfer of management data to and from the protocol device.                                                                                                                                                                                                                                                                    |

| DVAD[4-3]    | K9, K8                | LVCMOS Input<br>with P/D | <b>Management Address.</b> Device Address: DVAD[4:3] is the externally set physical address given to this device used to distinguish one device from another.                                                                                                                                                                                                                                   |

| JTAG Interfa | ce Signals            |                          |                                                                                                                                                                                                                                                                                                                                                                                                 |

| ТСК          | G3                    | LVCMOS input             | <b>Test Clock</b> . IEEE1149.1 (JTAG) TCK is used to clock state information and test data into and out of the device during the operation of the test port.                                                                                                                                                                                                                                    |

| TDI          | G4                    | LVCMOS Input<br>with P/U | <b>Test Data Input.</b> IEEE1149.1 (JTAG) TDI is used to serially shift test data and test instructions into the device during the operation of the test port.                                                                                                                                                                                                                                  |

| TDO          | H4                    | LVCMOS<br>Output         | <b>Test Data Output.</b> IEEE1149.1 (JTAG) TDO is used to serially shift test data and test instructions out of the device during operation of the test port. When the JTAG port is not in use, TDO is in a high impedance state.                                                                                                                                                               |

| TMS          | H3                    | LVCMOS Input<br>with P/U | <b>Test Mode Select.</b> IEEE1149.1 (JTAG) TMS is used to control the state of the internal test-port controller.                                                                                                                                                                                                                                                                               |

| TRSTN        | G5                    | LVCMOS Input<br>with P/U | <b>JTAG Reset.</b> IEEE1149.1 (JTAG) TRSTN is used to reset the internal JTAG controller.                                                                                                                                                                                                                                                                                                       |

| Miscellaneou | s Signals             |                          |                                                                                                                                                                                                                                                                                                                                                                                                 |

| CODE         | E6                    | LVCMOS Input<br>with P/U | <b>PCS Functions Enable.</b> When high, the Physical Coding Sublayer (PCS) functions are enabled. This pin is logically AND'd with MDIO register PCS_EN.                                                                                                                                                                                                                                        |

| ENABLE       | E9                    | LVCMOS Input             | <b>Device Enable.</b> Pulling this pin high will enable all outputs of the device. A low on this pin will tri-state all outputs of the device, and causes the serial outputs to be pulled to VDDA through 500 $\Omega$ . This signal must be externally held high during JTAG manufacturing test on the customer application board. See Appendix A for more details.                            |

| CTC_EN       | H5                    | LVCMOS Input<br>with P/U | <b>CTC Enable.</b> This pin is AND'd with the CTC register bit. Setting this pin to logic 1 activates the CTC FIFO. A low on this pin disables the clock tolerance compensation function. This function should only be activated in transceiver mode (CODE=1).                                                                                                                                  |

| TCLKSEL      | E8                    | LVCMOS Input<br>with P/D | <b>Independent Channel Transmit Clock Select.</b> A logic 0 selects latching of all channels synchronous to TCLKC. A logic 1 selects individual clocking. This pin bit is logically OR'd with the TCLKSEL input MDIO register bit.                                                                                                                                                              |

| RESET        | E10                   | LVCMOS Input<br>with P/D | <b>Chip Reset (FIFO Clear)</b> Pulling this terminal high re-centers the transmit skew buffers, receive channel synchronization FIFO's, and will reset MDIO flags to default settings. Reset should be asserted for 100 $\mu$ s after all power supplies and input clock frequencies are within specification. Alternatively, a soft reset could be issued after clock and power stabilization. |

| LPBK         | E5                    | LVCMOS Input<br>with P/D | <b>Loopback Enable.</b> When set high, TX+/– outputs are pulled to VDDA through 500 ohms. The serial TX+/– output data is internally looped to RX+/– inputs. External data applied to RX+/– inputs is ignored.                                                                                                                                                                                  |

## SIGNAL TERMINAL DESCRIPTION (continued)

| SIGNAL      | LOCATION                                                                                                                         | TYPE                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| PRBSEN      | F5                                                                                                                               | LVCMOS Input<br>with P/D | <b>PRBS Enable.</b> When this terminal is asserted high, the pseudo-random bit stream generator and comparator circuits are inserted into the transmit and receive data paths on all channels, respectively. If this pin is not used it can be tied to the GND reference. TX+– are transmitting 2 <sup>7</sup> -1 PRBS bit streams. RX+– are comparing incoming data to 2 <sup>7</sup> -1 PRBS bit stream. Results of the RX comparison can be read from the MDIO. |  |  |  |  |  |  |  |  |

| SYNCEN      | K10                                                                                                                              | LVCMOS Input<br>with P/U | <b>SYNC Enable.</b> When enabled, the TLK2226 byte-aligns incoming data on RX+/– positive RD (running disparity) commas (001 1111b). This pin is AND'd with the COMM_DET register bit.                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

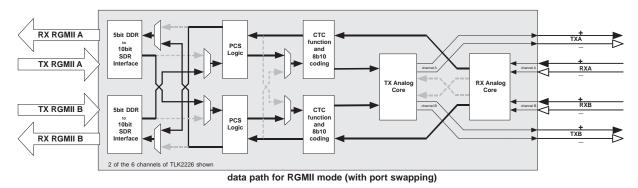

| SWAP        | K7                                                                                                                               | LVCMOS Input<br>with P/D | <b>Parallel Port Swap.</b> When enabled, the parallel port for channel B is routed to the serial port for channel A, and the parallel port for channel A is routed to the serial port for channel B. Likewise, the parallel ports for channels C and D, E and F are swapped. This pin is logically OR'd with the PORT_SWAP register bits.                                                                                                                          |  |  |  |  |  |  |  |  |

| REPEATA     | K5                                                                                                                               | LVCMOS Input<br>with P/D | <b>Repeater Mode Ports A, C, E.</b> When enabled, the serial data on the channel B receiver pins is repeated out on the channel A serial transmit pins. Likewise, Channel D serial receive data is repeated out on channel C serial transmit pins, and Channel F serial receive data is repeated out on channel E serial transmit pins. This pin is logically OR'd with the REPEATER register bits for channels A, C, and E.                                       |  |  |  |  |  |  |  |  |

| REPEATB     | K6                                                                                                                               | LVCMOS Input<br>with P/D | <b>Repeater Mode Ports B, D, F.</b> When enabled, the serial data on the channel A receiver pins is repeated out on the channel B serial transmit pins. Likewise, Channel C serial receive data is repeated out on channel D serial transmit pins, and Channel E serial receive data is repeated out on channel F serial transmit pins. This pin is logically OR'd with the REPEATER register bits for channels B, D, and F.                                       |  |  |  |  |  |  |  |  |

| RSVD        | J5                                                                                                                               | RESERVED                 | <b>Reserved:</b> This signal is reserved for TI internal testing. These should be connected to GND in customer applications.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| SGMII       | E7                                                                                                                               | LVCMOS Input<br>with P/D | <b>SGMII Mode</b> When asserted, enables SGMII mode. When low, SGMII mode is deasserted. This pin sets the default value of the SGMII register bit (16.4) on the falling (deasserting) edge of the RESET pin.                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Power and R | eference Pins                                                                                                                    |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| VDDQ        | B3, B6, B9, D5,<br>D8, L5, L8, N3,<br>N6, N9                                                                                     | Supply                   | HSTL I/O Supply Voltage. 1.5 V or 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| VDD         | F10, G10, G11,<br>H10, H11, J10                                                                                                  | Supply                   | Digital Logic Power: Provides power for all digital circuitry. Nominally 1.8 V.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| VDDS        | G1, J2                                                                                                                           | Supply                   | Secondary voltage LVCMOS I/O Supply Voltage 1.8 V OR 2.5 V OR 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| VDDA        | A11, B11, C11,<br>D11, E11, E12,<br>F11, J11, K11,<br>K12, L11,M11,<br>N11, P11                                                  | Supply                   | <b>Analog Power.</b> VDDA provides a supply reference for the high-speed analog circuits, receiver and transmitter. Nominally 1.8 V.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| VREF        | G2                                                                                                                               | Reference                | Voltage Reference- for HSTL reference                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| GNDA        | A14, B14, C14,<br>D14, E13, E14,<br>F14, G14, H14,<br>J14, K13, K14,<br>L14, M14, N14,<br>P14                                    | Ground                   | <b>Analog Ground.</b> GNDA provides a ground reference for the high-speed analog circuits, RX and TX.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| GND         | B2, B5, B8, D4,<br>D7, F6, F7, F8,<br>F9, G6, G7, G8,<br>G9, H2, H6, H7,<br>H8, H9, J1, J6,<br>J7, J8, J9, L4,<br>L7, N2, N5, N8 | Ground                   | <b>Digital Logic Ground.</b> Provides a ground for the logic circuits and digital I/O buffers.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

## DETAILED DESCRIPTION

## **REFERENCE CLOCK SYNTHESIZER (PLL)**

The TLK2226 employs a mature Phase Lock Loop (PLL) design in use for Gigabit Ethernet transceivers and high-speed serial links by Texas Instruments since 1997 on both standard products and custom ASIC designs. This PLL design is used to synthesize the serial line rate bit clock from the REFCLK input as well as generate clocks for the receiver sampling circuitry. The PLL and associated high speed circuitry is powered by the analog power supply pins (VDDA) with isolated grounds (GNDA). Care should be taken in providing a low noise environment in a system. It is recommended to supply the VDDA reference by separate isolated plane within the system printed circuit board (PCB). It is recommended that systems employing switching power supplies provide proper filtering of the fundamental and harmonic components in the 1MHz-10Mhz band to avoid bit errors from injected noise. It is strongly recommended that no PLL based clock synthesizer circuit be used as the source for the REFCLK. This could cause accumulation of jitter between the two PLL's

## **OPERATING MODES**

The TLK2226 has two operational modes with respect to the Physical Coding Sublayer (PCS) functions called RTBI mode and RGMII mode. The RTBI or RGMII mode is selectable via the CODE bit in MDIO register space or the CODE pin as described in Table 1. The CODE pin is gated with the internal CODE register such that setting the pin to a logic zero disables the PCS functions, setting the CODE pin to a logic one enables PCS functions and permits these functions to be disabled on a channel by channel basis via MDIO control. In addition, all PCS functions except the CTC FIFO may be enabled if the CTC FIFO is to be implemented in the protocol device. The CTC FIFO may be disabled by way of the CTC\_EN pin or the CTC\_EN bit in the MDIO register space. Besides the RTBI or RGMII modes, additional modes of operation include the serial repeater mode with CTC FIFO mode, serial repeater without CTC FIFO mode, RGMII port swap mode, and 1/10 rate for 100FX mode.

### **Table 1. PCS Operational Modes**

| CODE | OPERATING MODES                                                                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Low  | <b>RTBI mode.</b> Disables PCS functions for each channel. Refer to <i>Byte Alignment Logic</i> section, for additional description over this mode. |

| High | <b>RGMII mode.</b> Enables PCS functions for each channel. Data on the transmit and receive data bus is treated as un-coded data.                   |

## **RTBI MODE**

In RTBI mode, the transmit data bus for each channel accepts 5-bit wide encoded data on the transmit data bus pins. Data is latched on the rising and falling edge of the transmit data clock. The encoded data is then phase-aligned, serialized and transmitted sequentially beginning with bit 0 over the differential high speed serial transmit pins. The receive data bus for each channel outputs 5-bit wide data. Data is output relative to both the rising and falling edge of the receive clock.

data path for RTBI mode

Figure 14. RTBI Mode Block Diagram

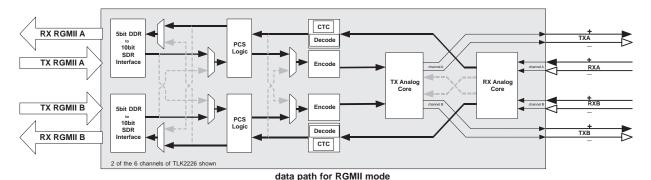

## **RGMII MODE**

In RGMII mode, the transmit data bus for each channel accepts 4-bit wide un-coded parallel data plus the two GMII control bits TX\_EN and TX\_ER (on bit4 of TDx[4:0]). Data is sampled on the rising and falling edge of the transmit clock. The data is first aligned to the reference clock (REFCLK), then 8B/10B encoded and passed to the serializer. The receive data bus for each channel outputs un-coded 4-bit wide parallel data plus the two GMII status bits RX\_DV and RX\_ER (on bit4 of RDx[4:0]).

Figure 15. RGMII Mode Block Diagram

In RGMII mode, all of the PCS functions are implemented as required by the IEEE802.3 specification, including the 8b/10b encoding, decoding, Clock Tolerance Compensation, insertion of the Start of Frame and End of Frame codes, and the auto-negotiation state machine. In RGMII mode, it is also possible to bypass the CTC FIFOs in which case the received data will be output with a recovered byte clock that remains in the clock domain of the received serial data stream.

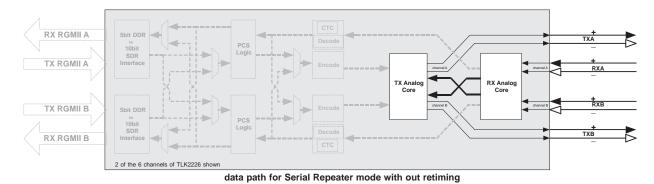

## SERIAL REPEATER MODE (WITHOUT CTC)

The serial repeater mode operation can be selected on a per channel basis. The serial inputs on one channel are transmitted back out serially on the adjacent channel. Channel A receive data is repeated out on channel B transmit while channel B receive data is repeated out on channel A transmit. In this manner channels A and B can form a full-duplex repeater. Likewise, channels C and D, and E and F can be used to form full-duplex repeaters.

Repeater mode for channels A and B can be chosen separately, if desired. That is, serial data received on channel A can be repeated out on channel B transmit pins without also choosing to repeat channel B serial receive data out on channel A. In fact, the repeater mode selection bit for a given channel may be thought of as simply selecting whether the data to be transmitted for that port comes from the parallel port for that channel or the serial data from the adjacent channel. In this way, a channel may be used as a normal RGMII or RTBI channel while the incoming serial data is also repeated out on the adjacent channel. When repeater mode for a given channel is selected, any data presented to the parallel transmit bus for that channel will be ignored.

While in repeater mode, the incoming serial data will still go through the deserializer function, and the PCS functions if enabled, and the deserialized data will still be presented out on the parallel transmit bus. Since the Clock Tolerance compensation functions are disabled in this mode, the data presented on the parallel port will reflect the CTC function being disabled as well.

Repeater mode without CTC is chosen by setting the repeater mode register bit active while also setting the CTC\_EN register bit inactive at the same time.

Figure 16. Serial Repeater Mode Block Diagram

In serial repeater mode, a clock/data recovery function (CDR) locks to the incoming data stream and then sends that data out on the transmit port of the adjacent channel. The CDR function will lock to the data stream so that Inter-Symbol Interference (ISI) jitter is filtered out from the retransmitted data. Retransmitted data will remain in the clock domain of the incoming data stream, since there is no clock tolerance compensation FIFO to adjust the data stream to the REFCLK clock domain. Since the CDR function will track any frequency wander on the data stream that is lower than the bandwidth of the CDR, any such wander components will remain in the retransmitted data stream. Also, since the jitter tolerance specification for the CDR function is such that the recovered bit clock must work with a minimum eye opening of 0.2513UI (equal to 201ps at 1.25GB/s), and the jitter generation specification for a transmitted data stream is 0.24UI (equal to 192 ps at 1.25Gb/s), it is not guaranteed that the re-transmitted serial data will meet the IEEE802.3 jitter generation specifications.

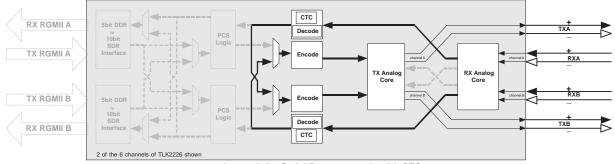

## SERIAL RETIMING REPEATER MODE (WITH CTC)